Bonjour JP,

Bonjour aussi à tous ceux qui suivent ce fil de discussion.

Dans la frénésie à vouloir à tout prix inverser à la volée le sens de comptage d’une cascade de 2 ou 3 boitiers compteurs, on a failli passer à coté des choses simples…

Soit un compteur normal, tout à fait normal, comme un compteur asynchrone, sur 3 bits pour simplifier.

Il compte de 0 à 7 et une fois arrivé à 7, il déborde au coup d’horloge suivant et repart de zéro : 0, 1, 2, 3, 4, 5, 6, 7, 0, 1, 2, 3, 4, 5, 6, 7, 0…

Maintenant la même série de décimaux exprimée en binaire :

000, 001, 010, 011, 100, 101, 110, 111, 000, 001, 010, 011, 100, 101, 110, 111, 000…

Toujours la même série binaire comme référence avec une copie dont on a inversé tous les bits (en bleu) :

000, 001, 010, 011, 100, 101, 110, 111, 000, 001, 010, 011, 100, 101, 110, 111, 000…

111, 110, 101, 100, 011, 010, 001, 000, 111, 110, 101, 100, 011, 010, 001, 000, 111…

A nouveau cette dernière série aux bits inversés accompagnée de sa traduction en chiffres décimaux :

111, 110, 101, 100, 011, 010, 001, 000, 111, 110, 101, 100, 011, 010, 001, 000, 111…

7 , 6 , 5 , 4 , 3 , 2 , 1 , 0 , 7 , 6 , 5 , 4 , 3 , 2 , 1 , 0 , 7 …

De toute évidence pour transformer un comptage normal en comptage à rebours, hé bien c’est ballot, il suffit tout simplement d’inverser tous les bits du compteur.

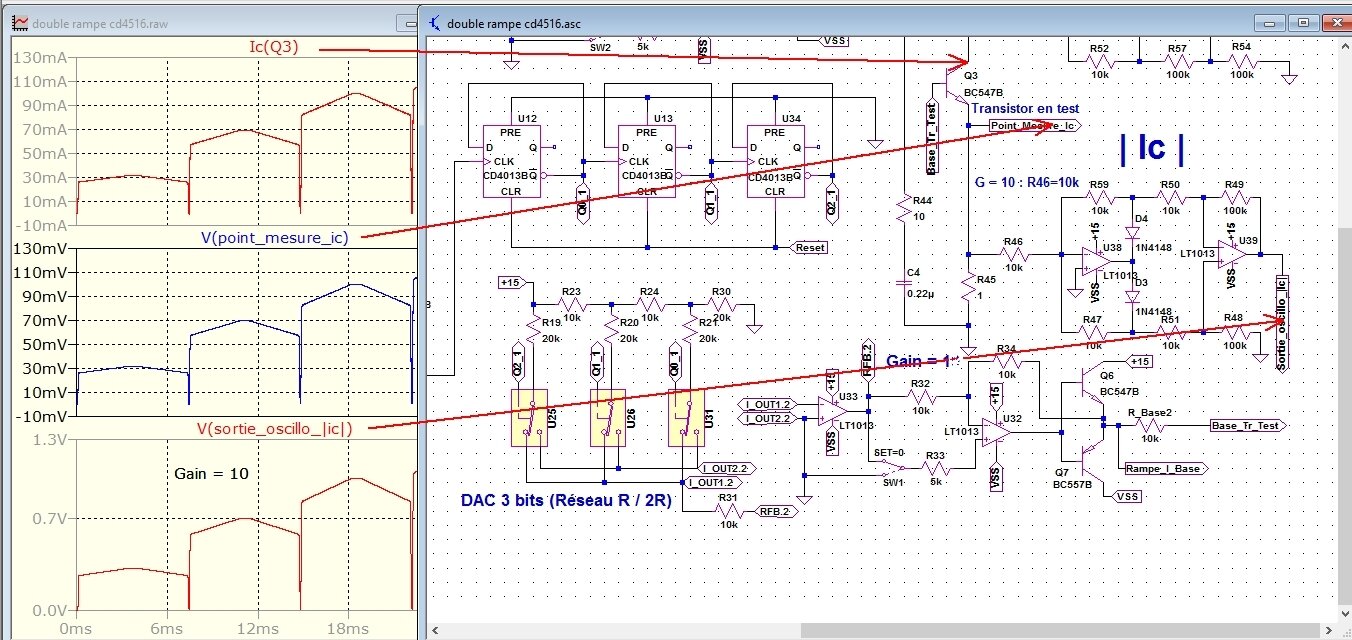

Et dans notre cas pour générer des signaux triangulaires avec le DAC, il faudra soit inverser les bits soit les utiliser tels quels en fonction de la parité du débordement.

000, 001, 010, 011, 100, 101, 110, 111, 000, 001, 010, 011, 100, 101, 110, 111, 000, 001, 010, 011…

000, 001, 010, 011, 100, 101, 110, 111, 111, 110, 101, 100, 011, 010, 001, 000, 000, 001, 010, 011…

0 , 1 , 2 , 3 , 4 , 5 , 6 , 7 , 7 , 6 , 5 , 4 , 3 , 2 , 1 , 0 , 0 , 1 , 2 , 3 …

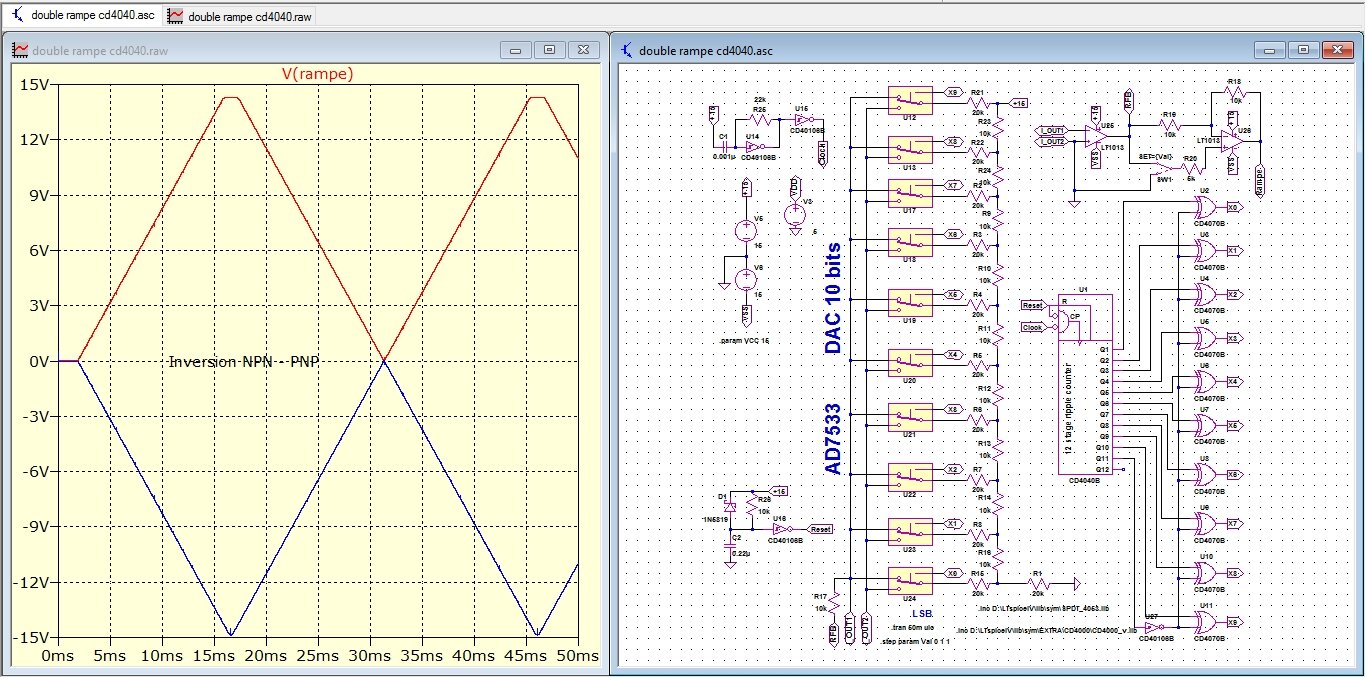

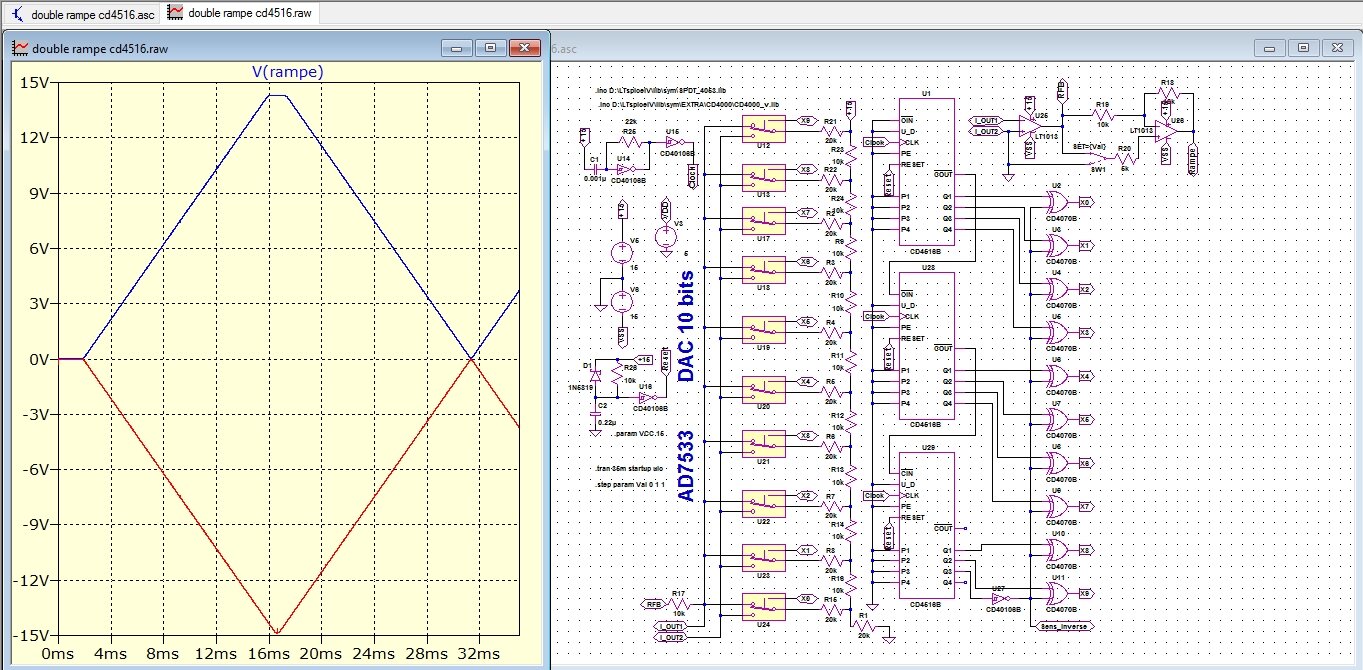

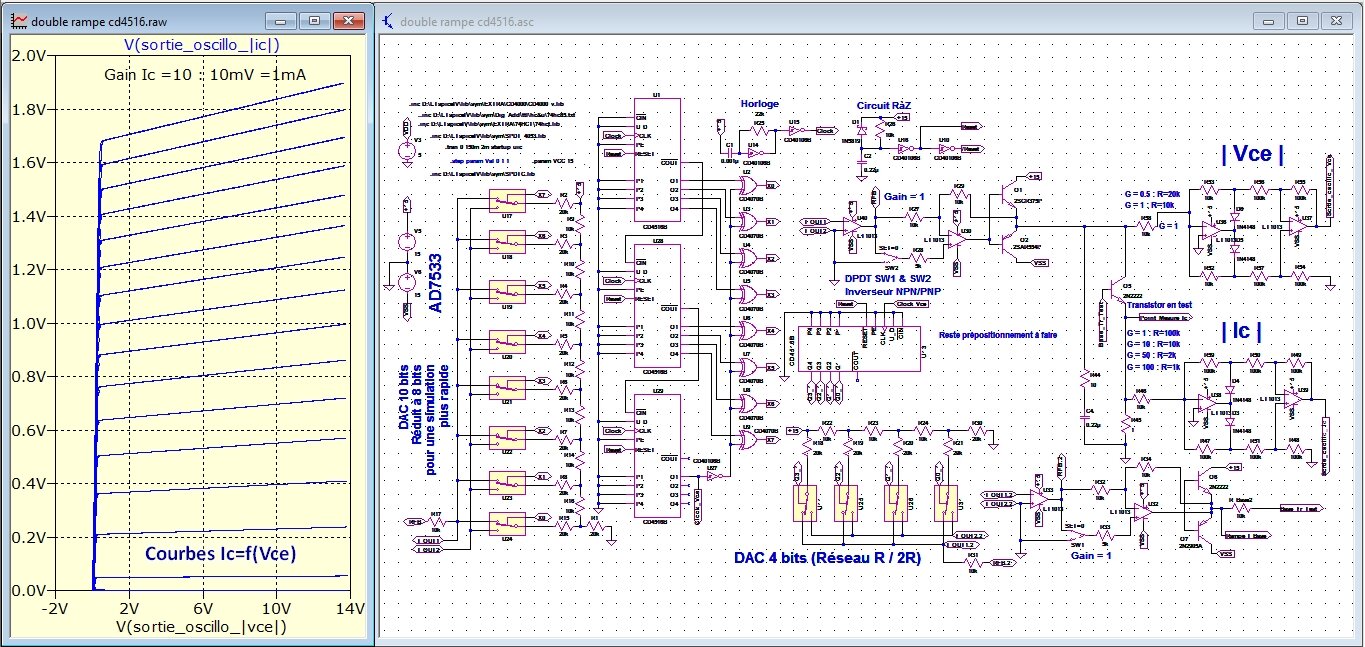

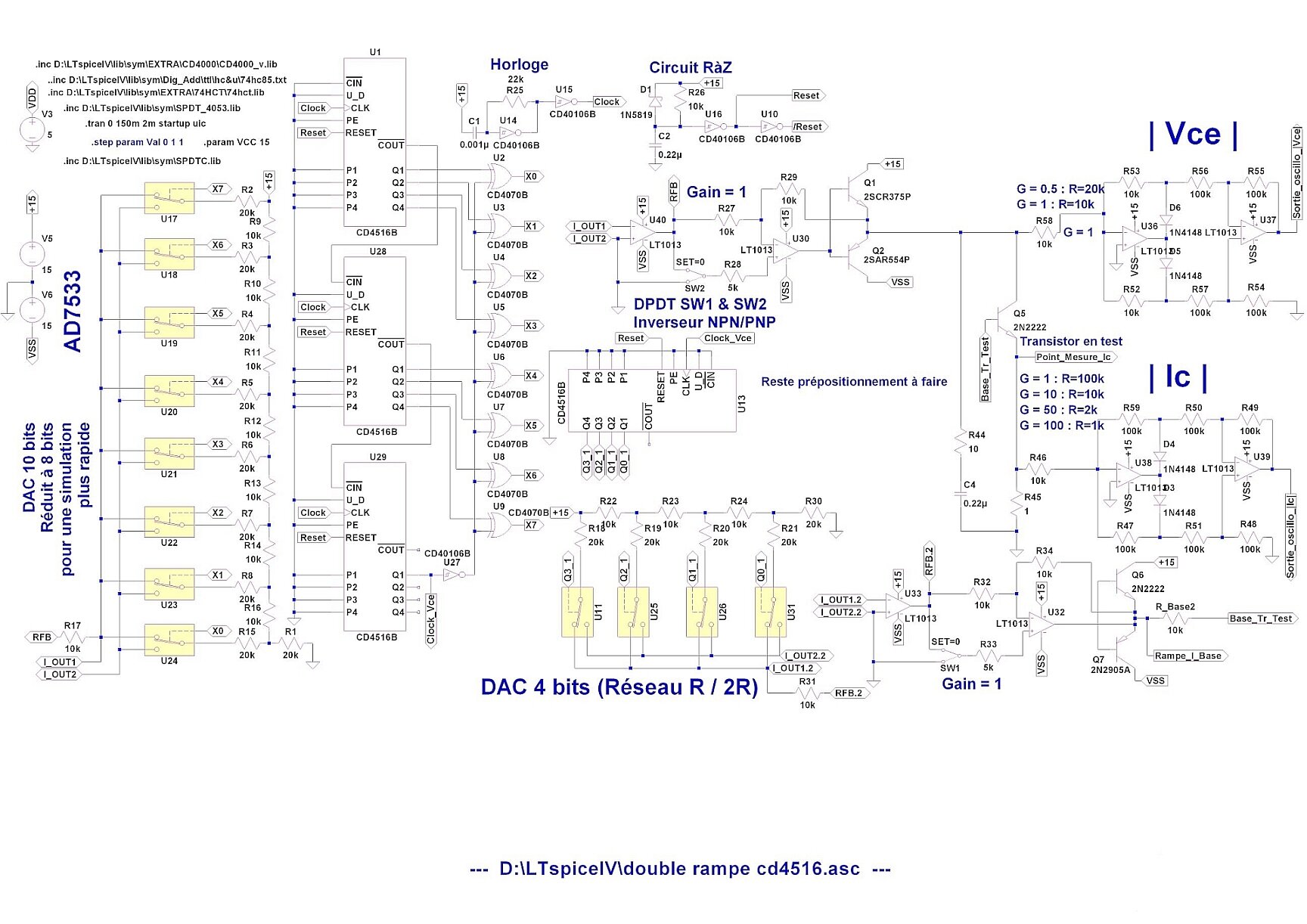

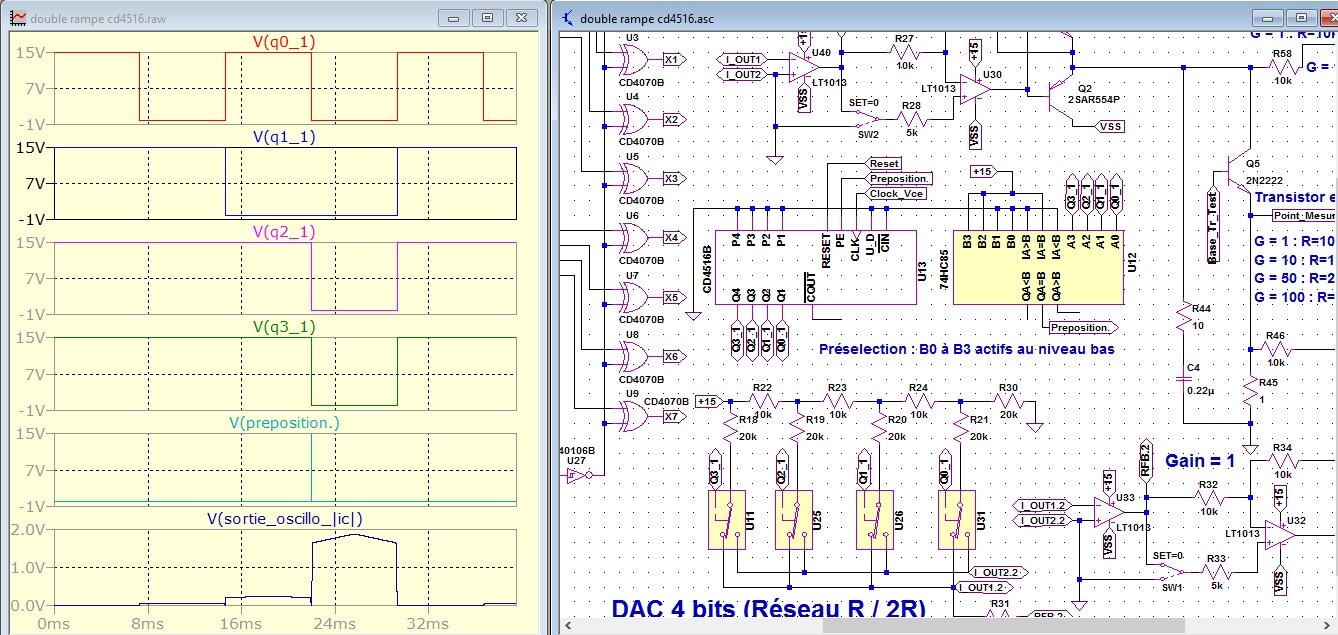

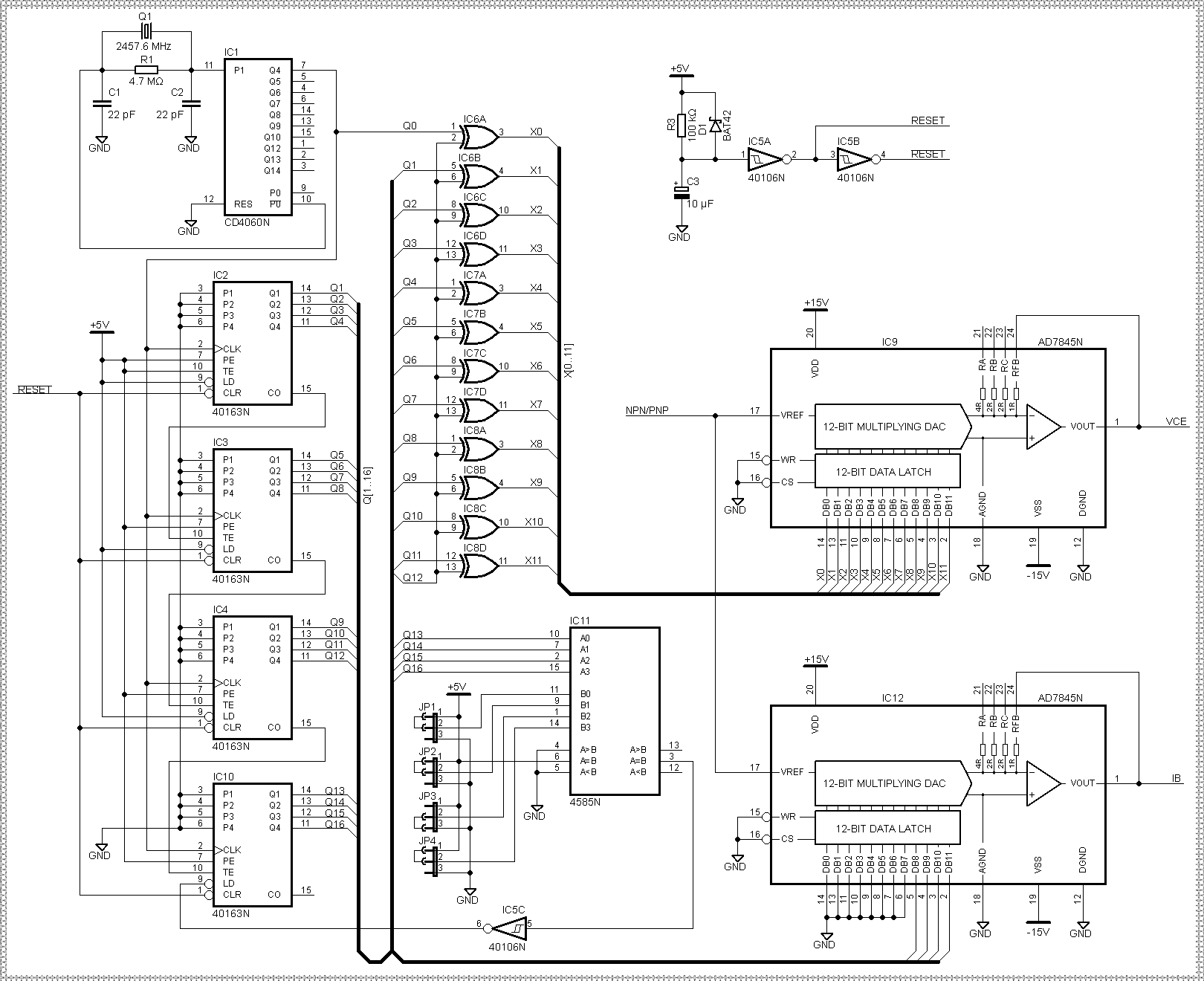

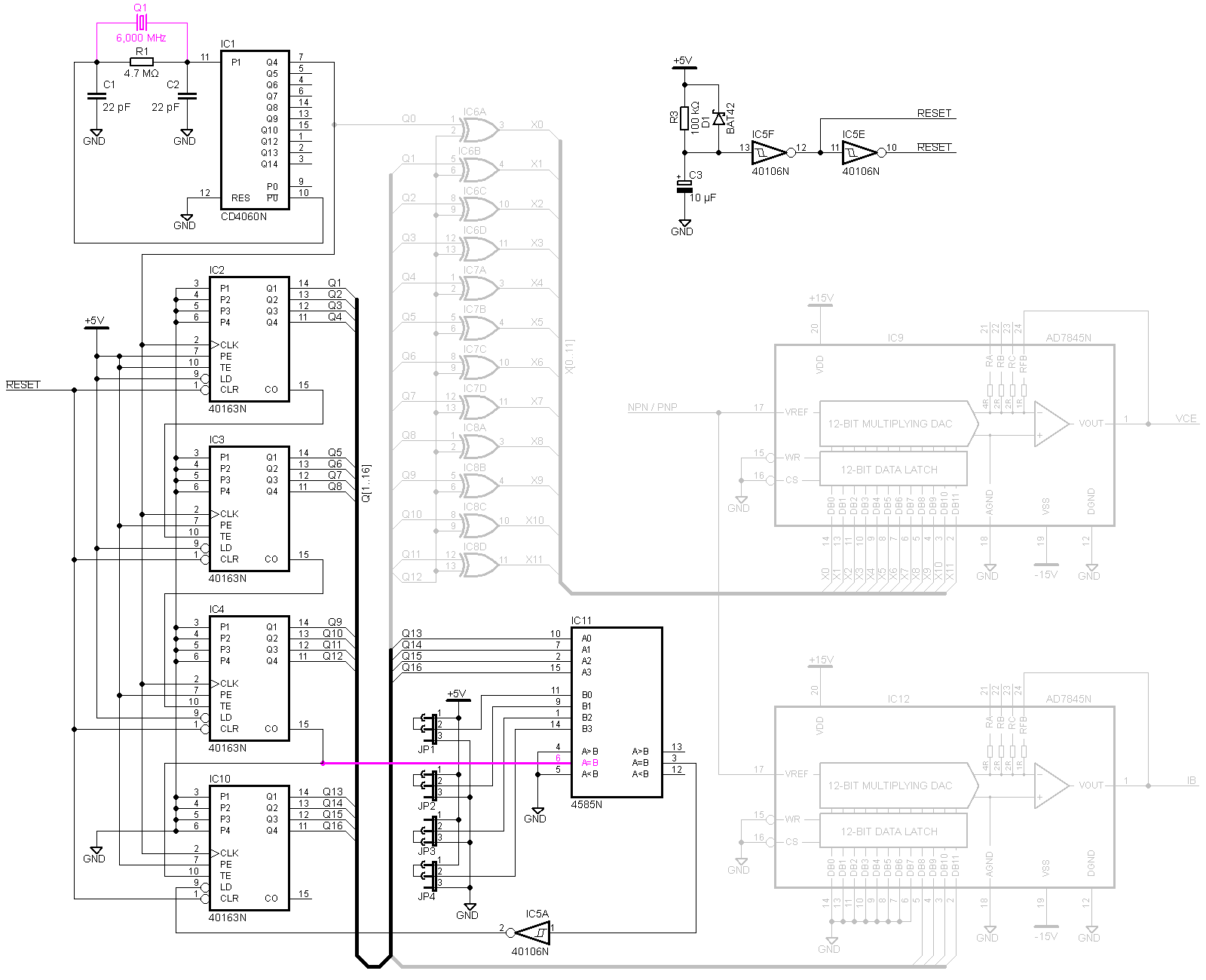

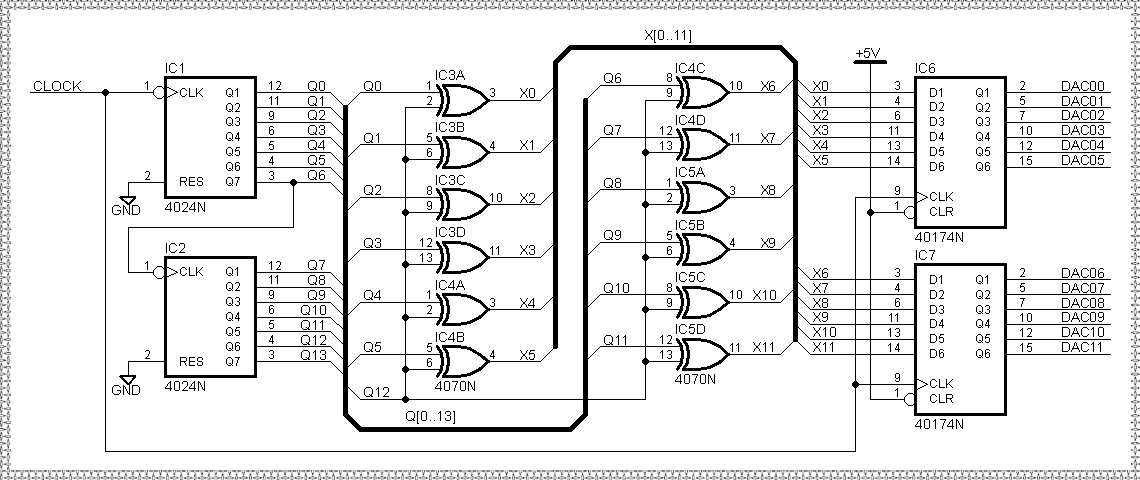

Et le schéma correspondant pour les 12 bits du convertisseur AD7845 :

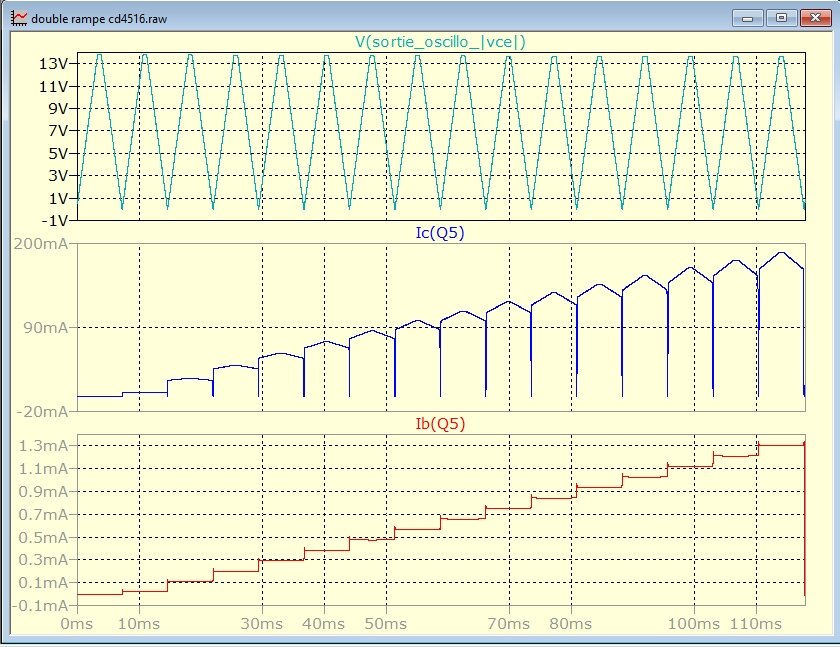

Détails, en fait c’est une adaptation du principe énoncé ici :* Les deux compteurs CMOS 4024 constituent un compteur asynchrone d’une largeur totale de 14 bits, bits Q[0…13].

Ce compteur ne s’incrémente que sur les fronts descendants de l’horloge unique.

- La batterie de portes XOR permet d’inverser simultanément les bits Q[0…11] du compteur. L’inversion est assujettie à l’état du bit Q12 de ce même compteur.

- Les deux sextuples latches des CMOS 40174 stockent les bits X[0…11] issus des portes XOR sur les fronts ascendants de l’horloge unique, garantissant ainsi un flux de bits exempt de « glitches » sur les entrées du DAC.

Doctsf (Modèles & Marques)

Doctsf (Modèles & Marques) Annonces

Annonces