Oui, j’avais pensé à utiliser la 4ème bascule JK en complément des marches d’escaliers.

Je vais voir pour l’oscillateur mais je pense garder le 555 et la porte « OU » ainsi que la « NAND » supplémentaire seront câblées en logique DTL.

Il me semblait bien que ce n’était pas possible de faire osciller une bascule JK. :mrgreen:

Dommage, ça aurait été une approche originale…

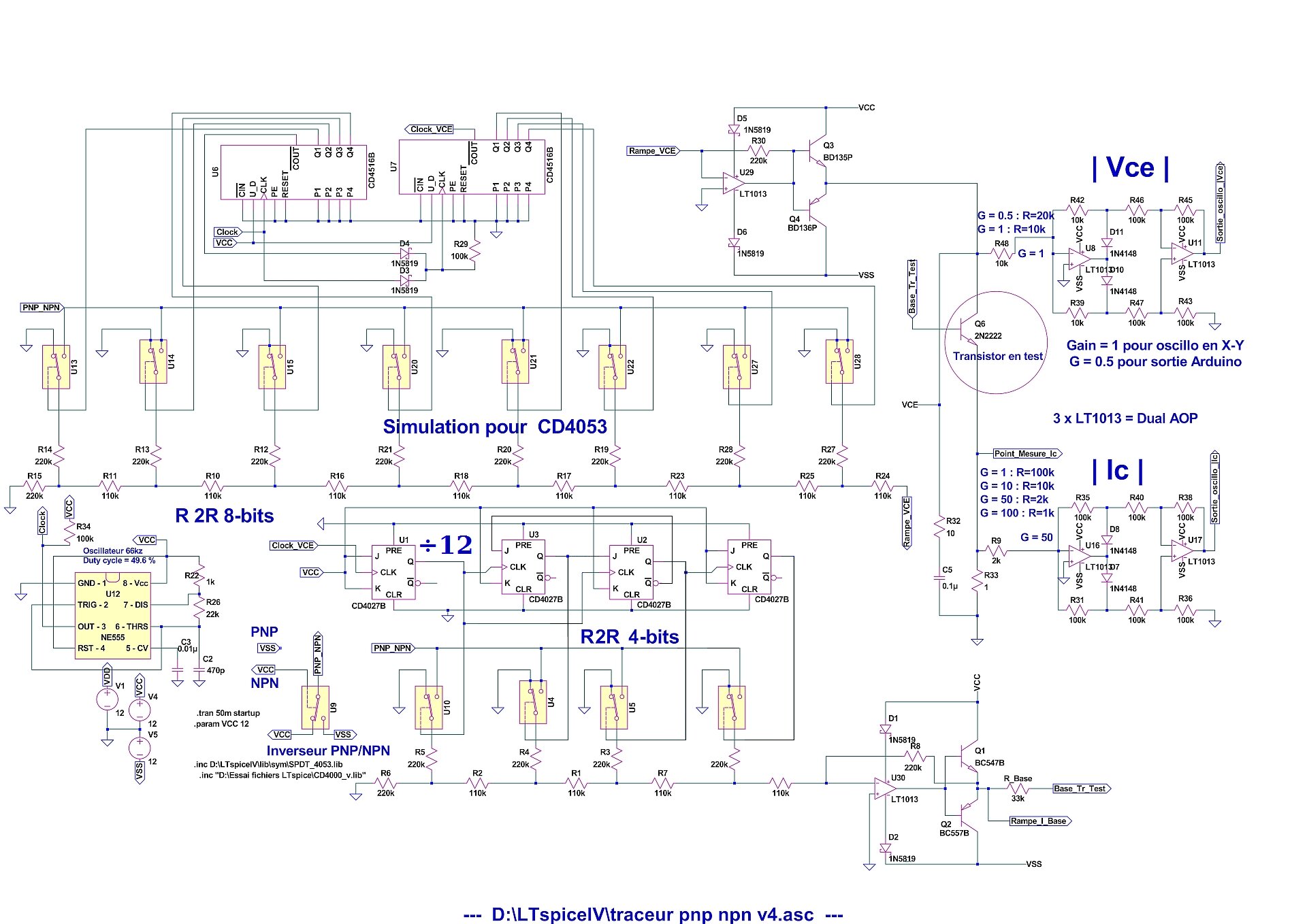

J’ai pensé que 15/16 marches d’escaliers pour Ib auraient trop surchargé l’affichage, aussi en afficher qu’une décade semblait plus raisonnable, donc 11/12 avec une modification minimale du compteur.

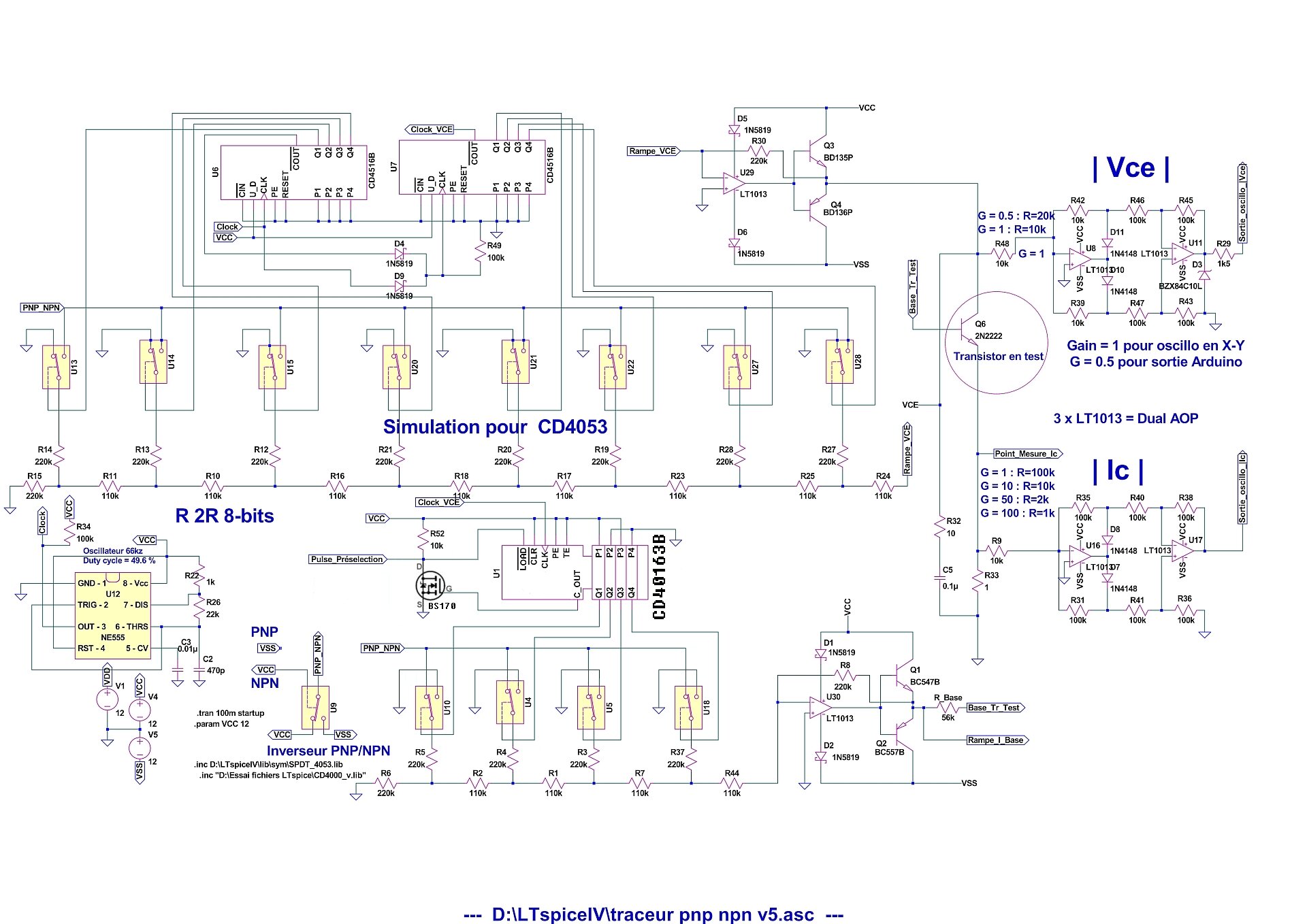

J’ai pas pu résister à la tentation de retoucher le schéma V4…

C’est marrant, j’ai fait la même modif que vous

Question : Avec quel soft vous modifiez mon jpg car le résultat est bluffant

J’ai retouché le schéma avec Paint (mspaint) et encore avec la version pour XP que j’ai rapatriée sous Windows 10, les nouvelles moutures me paraissant pas aussi pratique que celle-ci.

Suivant ce que je veux faire, j’utilise Paint, The Gimp, Paint.NET ou parfois FastStone Image Viewer. En fait j’utilise le plus approprié pour une manip donnée et je n’hésite pas à faire des copier/coller de l’un à l’autre pour obtenir le but recherché.

Version modifiée avec décade courant de base.

Ça commence à être l’usine à gaz

Bonjour.

Tout d’abord prendre le 7492 comme modèle de compteur par 12 était une erreur. S’il divise bien par 12, il a une manière de compter bien spécifique due au diviseur par 3 formé par les deux bascules centrales : 0, 1, 2, 3, 4, 5, 8, 9, 10 ,11, 12, 13, 0, 1, 2…

Ce schéma de compteur est donc inapproprié pour piloter un réseau R2R car les marches d’escalier ne seraient pas d’une hauteur égale.

Le remplacement des deux boitiers CD4027 par un boitier compteur BCD comme le CD4510 permettrait une certaine simplification… et éviterait les niveaux transitoires en sortie du réseau R2R car le compteur à base de CD4027 est asynchrone.

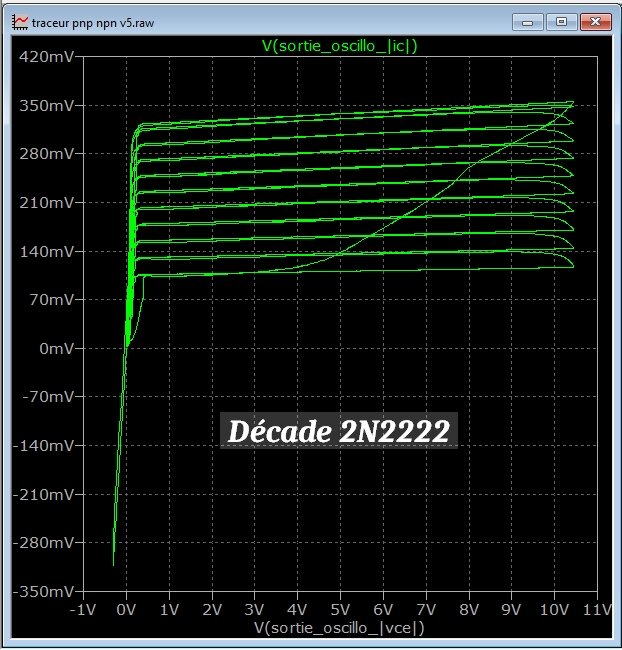

Employer un compteur par 10 pour générer la gamme de courant Ib ne couvre pas une décade entière de courbes car la valeur zéro ne produit aucun courant Ib, le tracé correspondant du Vce est plat puisque confondu avec l’axe des abscisses. En définitive il n’y a que 9 courbes qui sont significatives, celles qui correspondent aux valeurs de compteur 1…9.

Il faudrait alors un compteur par 11 pour pouvoir afficher la décade complète de courbes correspondant aux valeurs 1…10.

1ère solution : Utilisation d’un compteur binaire synchrone à prépositionnement synchrone comme le CD40163 ou 74HC163* En fait pour une simplification maximum, le compteur ne va pas compter de 0 à 10 mais décompter de 10 à 0. Les marches d’escaliers seront descendantes au lieu d’être montantes et les courbes seront tracées en commençant par les courants Ib de plus grande intensité.

- La valeur 10 (0AH ou 1010B) doit être câblée sur les entrées de prépositionnement.

- L’entrée « Load/ » doit être rebouclé sur la sortie « Carry Out » à l’aide d’un inverseur pour que le compteur soit rechargé avec la valeur prépositionnée (10 en l’occurrence) pile poil au moment où il aurait dû logiquement déborder de 0 à -1 (0FH ou 1111B).

- Le rechargement du compteur synchronisé avec le front montant de l’horloge devrait éviter l’apparition de valeurs transitoires sur ses sorties.

2ème solution : Utilisation d’un compteur synchrone comme le CD4522 (BCD) ou le CD4526 (binaire) :* Ce type de décompteur va aussi décompter mais de 10 à 1, le passage à zéro n’étant que très fugitif à cause du rechargement asynchrone quasi immédiat. Les marches d’escalier seront aussi descendantes et restreintes à 10 puisque la marche zéro est quasi inexistante vue sa fugacité.

- Idem pour le prépositionnement à 10 des entrées.

- Même principe, l’entrée PE (Preset Enable) doit être directement rebouclée sur la sortie « 0 » (Terminal Count) pour que le compteur soit rechargé avec la valeur prépositionnée immédiatement après avoir atteint zéro et ce indépendamment de l’horloge.

- Bien que le rechargement soit asynchrone, le fait de surcharger une valeur paire (10) sur une valeur nulle ne devrait pas produire de transistoire, ce qui ne serait pas le cas avec une valeur impaire comme 11. Démonstration : 1 (0001B) → 0 (0000B) → 11 (1011B), Le bit de poids le plus faible change deux fois d’état en passant fugitivement à zéro avant de reprendre l’état antérieur, chacun des trois autres n’étant pas impacté soit par ce qu’il reste à 0 (bit 2²) ou ne change d’état qu’une seule fois (bits 2¹ et 2³).

Bonjour,

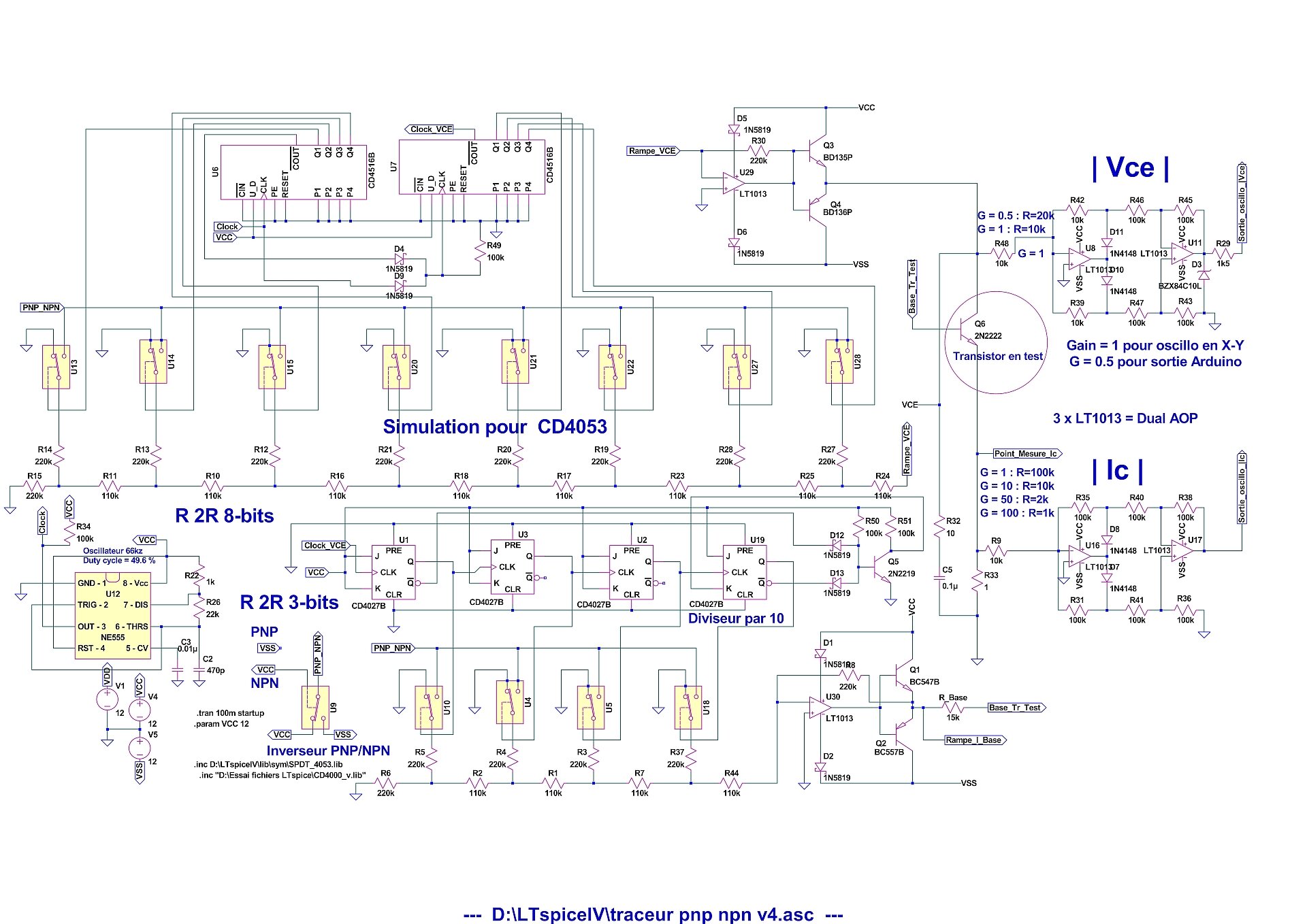

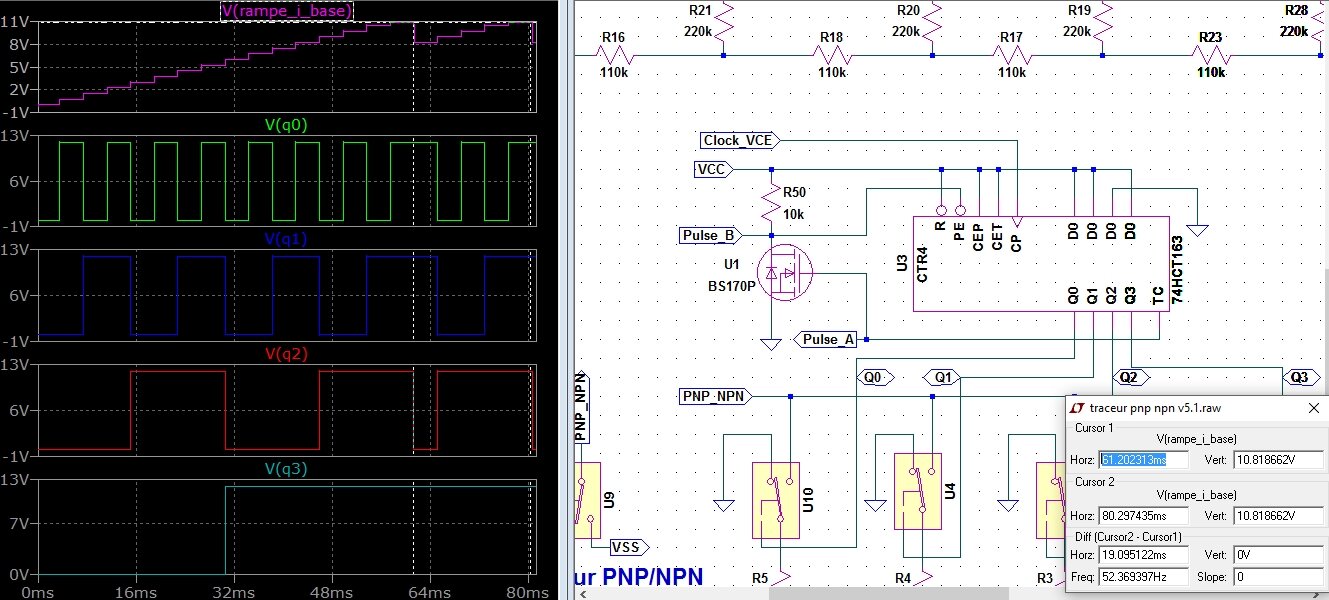

Le schéma précédent publié ne fonctionne pas, j’y ai cru mais c’est la fin du temps de simulation qui a arrêté les courbes :mrgreen:

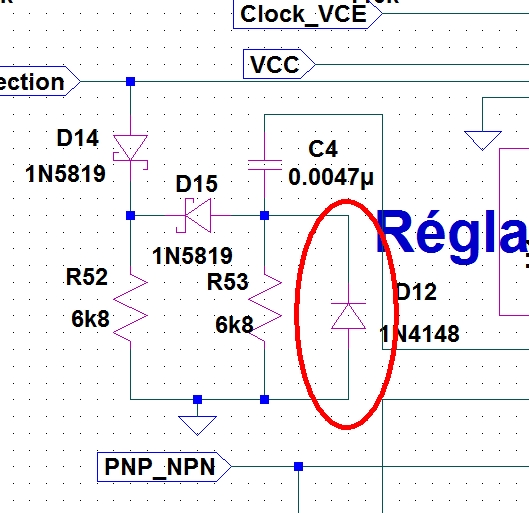

J’ai refait une autre variante en virant les CD4027 pour mettre un CD4029 (pas simple à apprivoiser au niveau des présélections).

J’ai du faire une pulse positive de quelques µs sur l’entrée P.E générée par la sortie C.OUT.

Au départ, j’avais fait une pulse à partir de VCC, mais a la fin du 1er cycle de comptage, on perdait la préselection et on repartait à zéro.

Ma foi, ça à l’air de fonctionner et ça permettra facilement de choisir le nombre de courbes à afficher.

Il me restera à inverser la sortie C.OUT pour l’envoyer en même temps sur le RST du 555 afin d’avoir un « one shoot » pour la sortie Arduino éventuelle.

Pour l’oscilloscope, je ne bloquerai pas l’horloge.

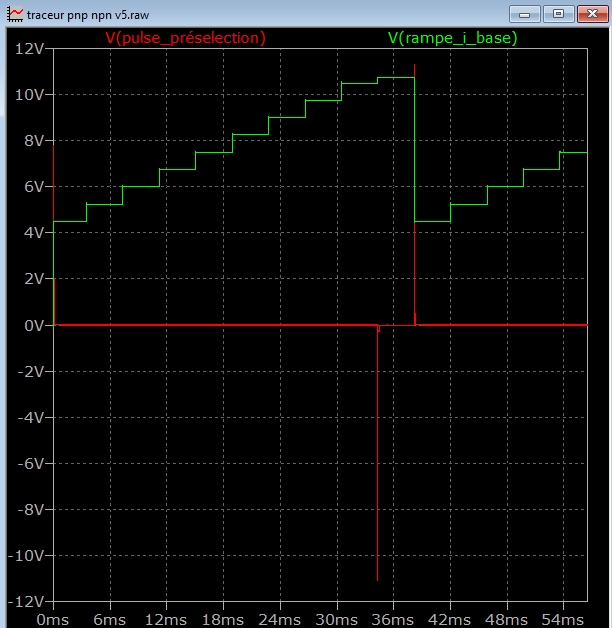

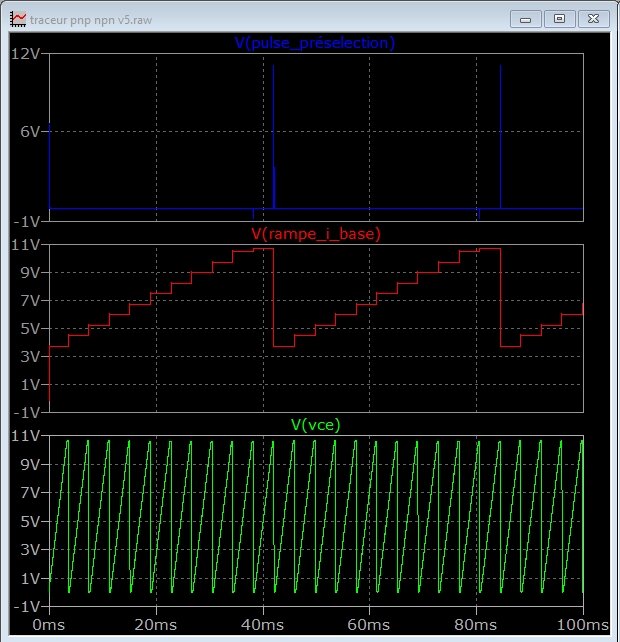

Ci-joint, nouveau schéma (version 5) ainsi que la courbe paliers base. Je viens de me rendre compte d’une pulse négative qu’il me restera à supprimer

Je pense que j’arrive au bout. Encore merci de vos lumières sans quoi, je serais encore en train de patauger… :mrgreen:

EDité 13h50

Suppression pulse négative ci-dessous

Pour terminer, 2 captures d’écran : 2décades complètes ainsi que la même chose en visu Ic=f(Vce).

Bonjour,

Felicitations pour cette aventure passionnante

Bien sur je suis tout cela et quelques remarques me viennent à l’esprit

-pour inverser la rampe PNP/NPN ne serait il pas possible d’utiliser un simple inverseur analogique on eviterait ainsi la serie d’inverseurs numeriques 0->+V devient 0-> -V

-utiliser un compteur a chargement asynchrone produit toujours des glitchs ce qui serait bien, me semble t il,

serai donc de prendre un compteur binaire 4 bits a chargement synchrone et pour realiser un compteur qui va de 1 à 11 on decode « 11 » sur les sorties qui charge « 1 » sur les entrees de preselection. je pense au 74161 ou 163

-je ne comprends pas les diodes 1n5481 qui alimente les ampli OP

A aucun moment je critique mais c’est je suis pris au jeu

Continuez

Sylvain

Merci pour les encouragements

-

Pour l’inversion NPN PNP, je ne comprends pas bien votre démarche. Qu’entendez-vous par inverseur analogique?

-

A mon avis, les glitchs ne sont pas problématiques pour cette utilisation, je ne fais pas un convertisseur de fréquence haute précision.

-

D’autre part, vu la fréquence du signal d’horloge (quelques dizaines de kHZ), le temps de propagation de quelques nano secondes sera peanuts et puis, j’ai suffisamment fait de modifications et j’aimerais passer au concret…

Pour les diodes dans le circuit d’alimentation des aop, j’ai bêtement pompé une partie d’un schéma Elektor sans me poser de questions.

Je présume qu’elle sont là en protection (l’ami Raffou pourra certainement disserter sur le sujet pour notre plus grand bien)

Bientôt, câblage en réel, mais ça ce n’est pas ma tasse de thé :mrgreen:

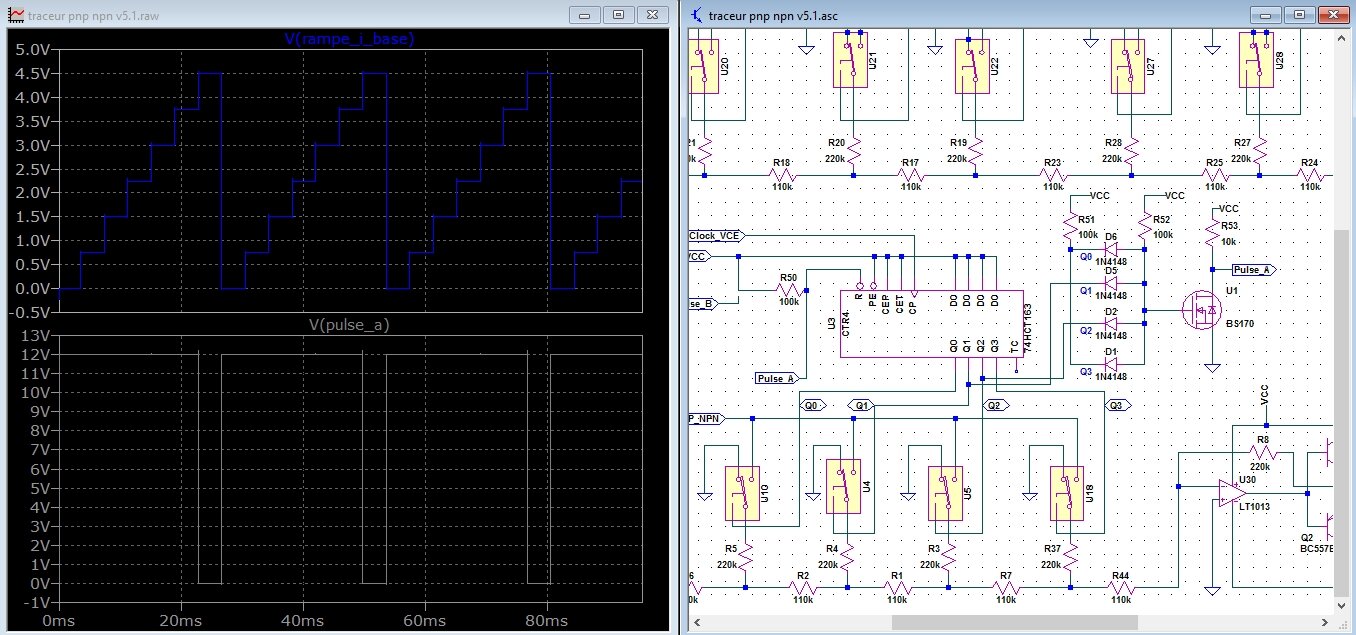

Tout d’abord mille excuses, je me suis encore fourvoyé et cette fois ci avec le compteur CD40163, j’ai du le confondre avec un autre. En relisant son datasheet je me suis rendu compte qu’il n’avait pas la faculté de décompter!

Si j’ai bien compris le schéma version V5, le compteur binaire CD4029 compte de 6 à 15 avant d’être rechargé à nouveau à 6. Ce qui explique la hauteur anormale de la première marche d’escalier sur les captures d’écran (? 3,5 volts au lieu de zéro sur la dernière capture).

Il existe un artifice simple pour contrer cette hauteur inusitée de la première marche, c’est de croiser les 2 entrées de chacun des 4 switches concernés. Ainsi au lieu de marches d’escaliers ascendantes correspondant aux valeurs de 6 à 15 du compteur, on obtiendra artificiellement des marches d’escaliers descendantes de 9 à 0 (15 - N) en sortie du réseau R2R avec une hauteur nulle pour la marche la plus basse.

Je me suis donc permis d’intégrer cette modification au schéma V5 et comme le dispositif pour prépositionner à 6 le CD4029 me m’inspirait pas particulièrement j’ai remplacé le tout par un CD40163 à chargement synchrone.* L’inverseur nécessaire est constitué d’un petit VMOS BS170 et d’une seule résistance.

- Le compteur compte de 5 à 15 car il est rechargé à 5, ce qui équivaut à une rampe descendante de 11 marches (de 10 à 0) dont la dernière à une hauteur nulle.

J’ai aussi repositionné la résistance R30, c’était OK avec la version V2 corrigée et redevenu NOK depuis le schéma V4.

Bonsoir Raffou,

Je n’ai pas trouvé de librairie spice pour le CD40163, c’est pourquoi j’ai utilisé un CD4029. Si vous aviez un modèle spice de ce circuit, je suis preneur

Je note l’astuce de croisement des switches.

C’est vrai que la solution du BS170 est plus « pro » que la mienne qui fonctionnait cependant :mrgreen:

Pour la résistance R30, c’est du à mon logiciel avec sa fonction d’accrochage auto et parfois ça me fiche le bazar, mais là curieusement je n’ai pas remarqué de différence à la simulation  .

.

Ce projet de traceur devient un véritable projet communautaire (à 2) et je m’en réjouis. Une fois terminé, avec un super PCB, ça va être top, d’autant que j’ai une boîte à chaussures de transistors sans marquage à trier dont quantité de germaniums pour lesquels j’ai d’autres projets en vue (je suis guitariste à mes heures perdues…). :mrgreen:

Bonne nuit.

Ce serait revenir à certaines des solutions employées dans les articles d’Electronique et Loisirs n°52 et 53 ainsi que dans celui d’Elektor n°368 de Février 2009, articles mentionnés au début de ce fil de discussion.

Pour mémoire :* Pilotage direct du réseau R2R par les compteurs.

- Ampli OP inverseur à gain unitaire en sortie du réseau R2R.

- Switch CMOS pour choisir entre la voie directe (sortie R2R) et la voie inversée (sortie ampli OP).

L’objectif était de « ne pas recopier bêtement un schéma de revue », la solution retenue avec des switches CMOS était pour le moins inédite et originale.

. C’est ce que j’expliquais dans mon avant dernier message au sujet de l’intérêt à remplacer le compteur asynchrone à base de CD4027 par un CD40163 / 74HC163 synchrone à chargement synchrone. Voir aussi la correction apportée dans mon dernier message avec le schéma V5 retouché par mes soins.

Moi non plus, cette configuration a été pompée sur le schéma du traceur de courbes CH-012 joint dans un des messages de lolo17 au début de ce fil de discussion.

C’étaient des diodes 1N4148 à l’origine et non pas des Schottky. Elles avaient peut-être une utilité sur le CH-012, mais avec ce nouveau schéma, ça reste à démontrer… Personnellement je les supprimerai!

Disposer les CD4025 en « parallel clocking » comme le suggérait Yves07 serait alors envisageable et permettrait de supprimer D4, D9 et R49.

Avez vous essayé de rechercher dans les libraries pspice? Ltspice devrait être capable de les lire si j’en crois ce que j’ai lu sur le net.

Sinon n’existerait-il pas une librairie pour le 74HC163 ou le 74HCT163 ? c’est le même brochage et fonctionnellement c’est le même compteur avec des temps de propagation moindre.

Disons que c’est plus « électroniquement correct » d’intégrer les transistors de sortie dans la boucle de contre-réaction ainsi on est assuré que le gain de l’ensemble est stable ou insensible à la valeur de l’impédance de charge.

Bonjour à tous,

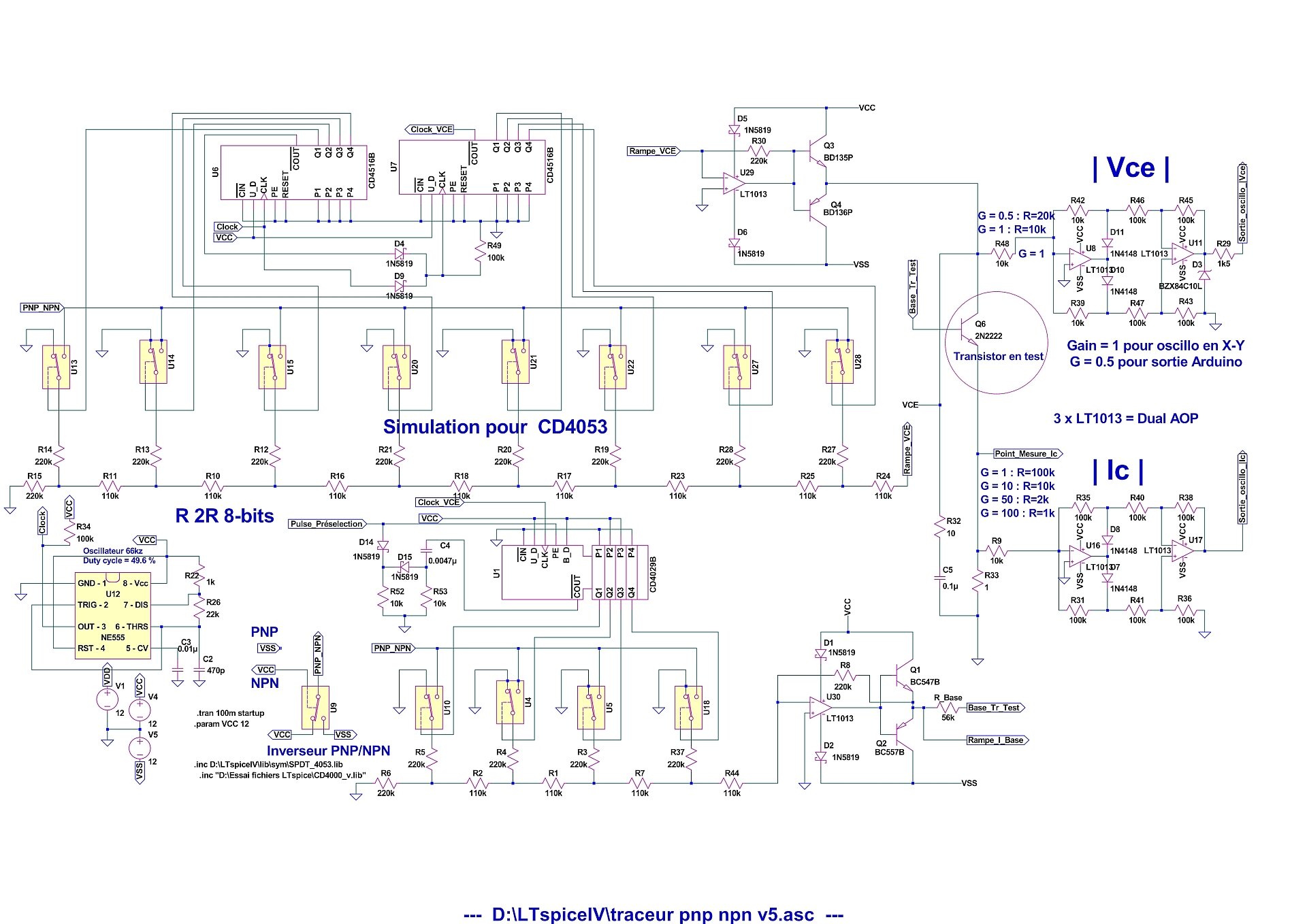

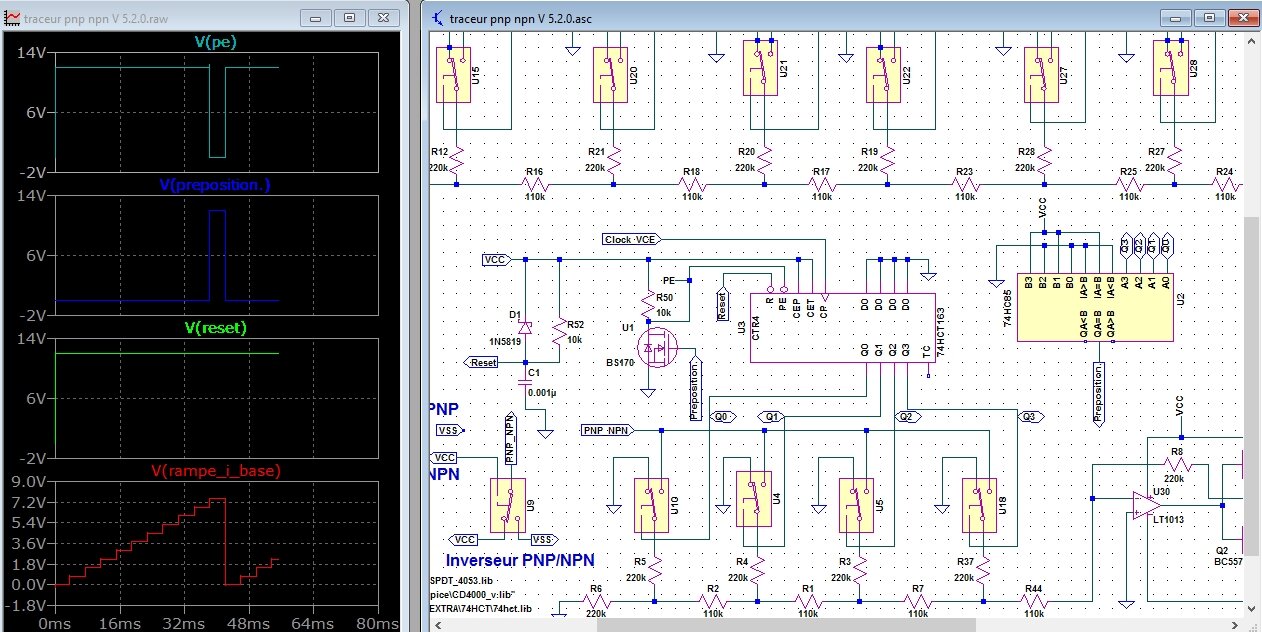

Ce matin, simulation avec un 74HCT163

Et bien, ça ne marche pas mieux qu’avec le CD4029!

Le fait de présélectionner le comptage positionne les sorties correspondantes à 1 et le démarrage de la rampe se fait à la valeur de tension prédéfinie.

Dans le cas ci-dessous, pour 4 steps de valeur unitaire 0.73V (VCC/15 = 0.73V), on va démarre à (15 - 4) x 0.73 = 8.03V

Et comme il n’y a en plus pas de Reset à la mise sous tension (que j’avais pris en compte avec le CD4029), le premier balayage démarra à 0 et se fait sur les 15 steps.

J’ai bien l’impression que le fonctionnement synchrone va tomber à l’eau.

Je pense faire une présélection avec une porte NAND sur les sorties Q0 à Q3 en fonction de mon choix et envoyer la pulse sur le Master Reset.

Je ne vois pas d’autre solution simple à mon niveau de connaissances.

Allez, une ch’tite capture d’écran pour la forme…

Modification effectuée ça me convient comme ça mais je vais remettre le CD4029 qui permet la décade ou le binaire et une possibilité UP/DOWN sauf si l’ami Raffou trouve une solution avec un compteur synchrone

Bonjour à tous,

Parlons plutôt de prépositionnement à la mise sous tension, j’avais complètement occulté le fait que le compteur démarrerait sur une valeur aléatoire, ici c’est peut être le simulateur qui impose la valeur zéro par défaut.

En voici une nouvelle plus souple que celle que vous avez imaginée, elle fait appel à un boitier comparateur CD4063, CD4585 ou 74HC85 sur les entrées duquel on programme le nombre de marches à la demande. Elle nécessite toujours le même compteur CD40163 ou 74HC163 pour bénéficier du rechargement synchrone.

Apparemment, le CD4585 semble être plus rapide que le CD4063, par contre son brochage est différent du 74HC85 alors que celui de CD4063 est compatible avec ce dernier.

J’ai créé un circuit RC de reset dans le coin en bas à droite, comme ça on est sûr que le compteur CD40193 démarrera toujours de zéro

A la mise sous tension, le compteur compte de 0 jusqu’à la valeur positionnée sur les entrées « B » du comparateur (ici 10) puis est réinitialisé au top d’horloge suivant par le chargement de la valeur zéro programmée en dur sur ses entrées de prépositionnement. Il compte donc indéfiniment de 0 à 10 inclus pour générer une rampe de 11 marches ascendantes avec une hauteur nulle pour la toute première.

Bonjour,

Cela devient passionnant

Ci joint pour information un simulation d’un ampli que l’on choisit inverseur ou pas par l’entree SEL

c’est un montage peu connu mais à retenir dans un coin,qui pour moi simplifierai bien cette realisation

De mon cote j’aimerai vous suivre plus mais helas pas tres familier avec LTspice

Pourriez me transmettre votre code source ?

et de plus , si possible ,les bibliotheque qui vont avec mais saurai je les installer ?

je n’ai jamais fait de numerique en simulation à part en logique programmable qui n’est pas de mise ici

Je reste bien entendu d’accord avec rafou sur l’interet de la logique synchrone

A plus peut etre

Sylvain

Bonjour Sylvain,

Pour ne pas encombrer le fil de discussion, on peut dialoguer par email au sujet de LTspice.

On pourra échanger les fichiers et les librairies et je pourrai te montrer 1 ou 2 trucs…

Je ne propose pas d’ouvrir un fil de discussion Spice sur le forum car il me semble que ce n’est pas l’endroit (quoique on peut tout à fait simuler des circuits à tubes) et qu’ à mon avis peu de membres seraient intéressés.

Donne moi ton adresse mail par MP si tu es intéressé.

J’ai jeté un œil sur ton fichier spice, ça fonctionne mais la rampe négative générée est descendante :mrgreen:

Ça marche!

Bravo Raffou

Doctsf (Modèles & Marques)

Doctsf (Modèles & Marques) Annonces

Annonces